Cela ne reste qu’une rumeur et si le choix d’augmenter cette mémoire cache L3 semble un moyen logique et intéressant pour Intel de faire évoluer les performances de ces puces, cela ne reste néanmoins pas un élément assuré à 100%.

Tremont1, nom de code de la future génération d’Atom chez Intel, pourrait donc embarquer plus de mémoire cache L3. Si vous êtes attentif aux billets du blog, vous constaterez souvent qu’en plus du nombre de coeurs et des fréquences des puces je mentionne souvent cette fameuse mémoire cache pour identifier les processeurs. Cette mémoire est importante au sein du complexe de calcul qu’est un processeur moderne.

Cette mémoire « L3 » signifie qu’elle est au troisième niveau de la partie qui effectue des calcul. Chaque « étage » de mémoire s’éloigne un peu plus des coeurs d’un processeur. Ainsi la mémoire cache L1 est très proche, la mémoire L2 est un peu plus distante et la mémoire L3 encore un peu plus éloignée. Le problème étant que plus on approche cette mémoire du coeur de la puce, moins il est possible d’en ajouter pour des raisons techniques et économiques.

Sur un processeur comme le Core i7-8565U par exemple, on a trois niveaux de mémoire cache : Le L1 est composé de 2 modules de 128 Ko. Le L2 de 4 modules de 256 Ko et le L3 de 4 modules de 2Mo. Les caches L1 et L2 sont intégrés juste à côté des coeurs et n’ont donc que peu de place pour s’y loger. Leur capacité est donc assez faible. Le cache L3 est séparé des coeurs et les « entoure » en général, il peut donc être de plus grande capacité. Chaque cache correspond en général à une capacité de base multipliée par le nombre de coeurs.

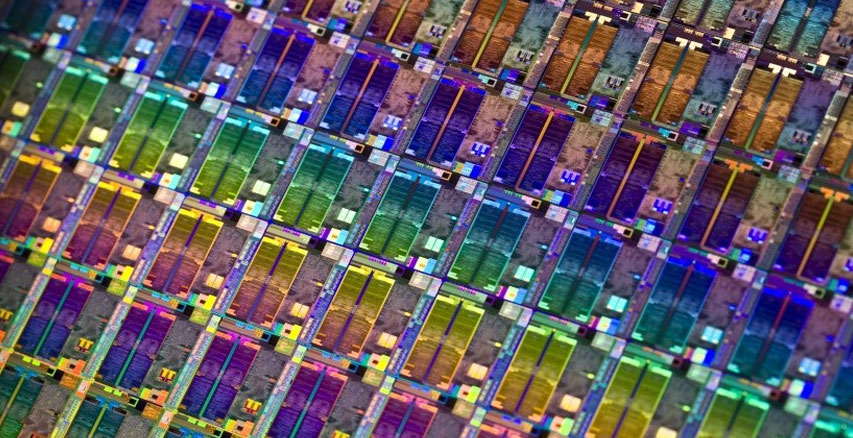

Un wafer Gemini Lake en gros plan avant découpe

Le cache étant directement intégré au processeur, il conditionne la rentabilité de celui-ci. Plus le cache est grand, plus il impacte le nombre de puces qu’une même galette de silicium pourra donner. Proposer un cache élevé impacte donc le coût de production des processeurs assez fortement.

A quoi sert ce cache et pourquoi est t-il si important ? Le cache sert à gérer des instructions au plus près des coeurs. Quand un coeur a quelque chose à calculer, il va se référer au cache. Plus celui-ci sera proche, plus il pourra effectuer un calcul rapide. Le cache L1 est donc très sollicité pour des calculs, puis le cache L2 et enfin le cache L3. Avec un processeur proposant 2Mo de cache par coeur en cache L3, la puce a de quoi stocker beaucoup de données pour effectuer ses calculs.

Rester sur la puce, sur le DIE même du processeur, pour piocher les éléments à calculer permet de ne pas aller les chercher sur la mémoire vive. Cela évite une circulation de données et permet de profiter de vitesses de calcul autrement plus impressionnantes que si il faut aller puiser sans cesse des données sur la mémoire vive globale de la machine. Le rôle de cette mémoire est donc capital dans les performances globales d’un processeur. Plus elle est grande, plus le processeur pourra profiter de sa capacité de calcul.

Le Goldmont Plus des Atom Gemini Lake avec 4 Mo de cache L2

Vous comprenez donc pourquoi cette rumeur d’une arrivée de mémoire cache L3 sur les Atom Tremont est importante. Si vous prenez les Gemini Lake actuels comme les Celeron N4100 par exemple. Leur architecture Goldmont Plus n’embarque pas de cache de troisième niveau. Ils sont, par contre, bien équipés en cache L2 avec 4 Mo. Le double des puces Godmont Apollo Lake qui n’embarquaient donc que 2 Mo de cache L2.

L’arrivée d’un troisième niveau de cache serait donc une nouveauté pour toute la gamme Atom. Un changement qui apporterait encore plus de performances à l’ensemble des puces avec évidemment des possibles contrecoups économiques et techniques.

Si Intel a toujours évité l’emploi d’un troisième niveau de cache dans ses puces Atom, c’est probablement pour éviter d’augmenter leur coût. Chaque Wafer pouvait proposer un maximum de processeurs exploitables, ce qui permettait de garder des solutions à prix très abordable. Augmenter la taille des processeurs avec cette mémoire supplémentaire aurait fait baisser ce ratio et donc pourrait en toute logique augmenter le prix des futurs Atom Tremont.

Exploitant la technologie Foveros, les Tremont pourraient inaugurer une nouvelle voie de travail pour Intel. Une solution permettant de conjuguer le prix et les capacités des puces. Avec Foveros, il est possible d’ajouter des éléments en étage les uns par dessus les autres comme le montre cette vidéo. La partie classique du processeur avec ses coeurs, son circuit graphique, ses contrôleurs ses caches L1 et L2 seraient sur le même étage. Le cache L3 pourrait donc se trouver sur un autre étage du dispositif. De telle sorte que le wafer de base produisant les processeurs aurait toujours la même rentabilité, le cache L3 serait produit à part et ajouté ensuite. Une solution qui préserverait la rentabilité de production des usines les plus coûteuses d’Intel.

Second point à prendre en compte, la destination des puces. Intel vise des machines mobiles et/ou compactes avec l’Atom. L’augmentation de taille ne sera vraisemblablement pas un problème mais il est possible que la note énergétique soit plus salée. Le TDP des solutions Gemini Lake comme le N4100 restait à 10 watts malgré le doublement du cache et l’augmentation de fréquence Turbo par rapport à Apollo Lake. Est-ce que Tremont pourrait rester dans cette enveloppe thermique avec un cache L3 supplémentaire ? Intel pourrait avoir recours à un artifice intéressant pour limiter la consommation en énergie de ces futurs Atom.

En permettant la désactivation d’une partie ou de la totalité du cache si il n’était pas nécessaire, les processeurs pourraient réduire leur besoin en énergie. En pratique, je ne pense pas que l’impact soit énorme, les applications actuelles sont gourmandes en cache et je ne vois pas trop dans quel scénario un système ferait l’impasse sur la possibilité de stocker des instructions de cette manière.

Il est également possible que cette arrivée d’un cache L3 ne concerne pas toutes les puces Atom mais uniquement les modèles sédentaires, ceux pour qui la consommation ne serait pas un souci.

Tremont est prévu pour 2019 et on devrait en savoir plus d’ici quelques mois maintenant. La suite prévue pour l’Atom est dans la génération Gracemont qu’Intel positionne pour 2021 dans son calendrier de sorties. Il va sans dire que si les processeurs Tremont bénéficiaient d’un troisième niveau de cache, on imagine assez mal comment les Gracemont ne pourraient pas en proposer.

Notes :

- Tremont est le nom de code de la micro-architecture de la puce, comme Goldmont. Il n’existe pas de puce Tremont ou Goldmont commercialement parlant. Intel utilise des noms de plateformes comme Gemini Lake ou Apollo Lake qui reprennent ces micro-architectures pour en faire des familles de processeurs.

| 2,5€ par mois | 5€ par mois | 10€ par mois | Le montant de votre choix |

Un refresh de Goldmont Plus devrait être là avant (sans remplacer Tremont en principe).

on est bien loin des premiers celeron sans mémoire cache des années 2000.

Sur les Atom, la MMU est il me semble aussi un problème faute de pouvoir faire une page unique pouvant contenir tout le kernel (faute de TLB de taille variable). Avoir des miss à ce niveau est normalement évité comme la peste.

Les Atom étant désormais déclinés au coeur de SoC dédiés infra télécom (avec également une partie accélérateurs réseau + DSP pas sans rappeler ce que fait Freescale/NXP ou Cavium) censés remplacer les Xeon qui font surtout un chauffage performant… possible de voir des retombées au delà. Enfin si Intel arrive à les faire fonctionner un jour comme attendu.

Encore un article complet, bien écrit et où on comprend tout.

Merci Pierre

@Blanquette:

Qui est censé avoir quitté l’école trop tôt? Celui qui explique en faisant tout pour le rendre compréhensible un point de micro-architecture ou celui qui na’arrive pas à placer un seul qualificatif adapté?