Risc-V est un bébé, l’architecture est très jeune et si elle attire beaucoup les regards, elle n’a probablement pas encore dévoilé qu’une fraction de son potentiel. Pour SiFi,ve cela ne fait aucun doute, à long terme elle passera devant ARM.

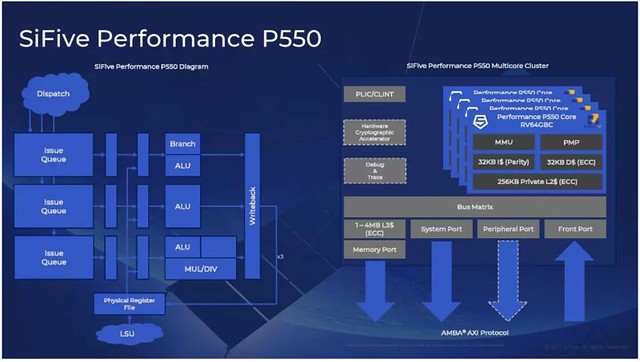

Le SiFive P550 est annoncé comme une solution performante et suffisamment intéressante pour qu’Intel l’intègre sans ses futurs processeurs Horse Creek. Pour le moment, nous n’avons pas beaucoup d’informations sur ces futurs processeurs Intel et il est toujours impossible de savoir si il s’agira d’une puce hybride mélangeant RISC-V et x86 ou une puce RISC-V pure. Mais il semble que cette future solution gravée en 7 nm soit suffisamment pertinente pour Intel pour que le fondeur veuille racheter SiFive… Le Performance P550 utilise la microarchitecture U84 de SiFive et peut être associé par 4 pour le même encombrement physique qu’un seul coeur Cortex-A75 tout en offrant une meilleure efficacité.

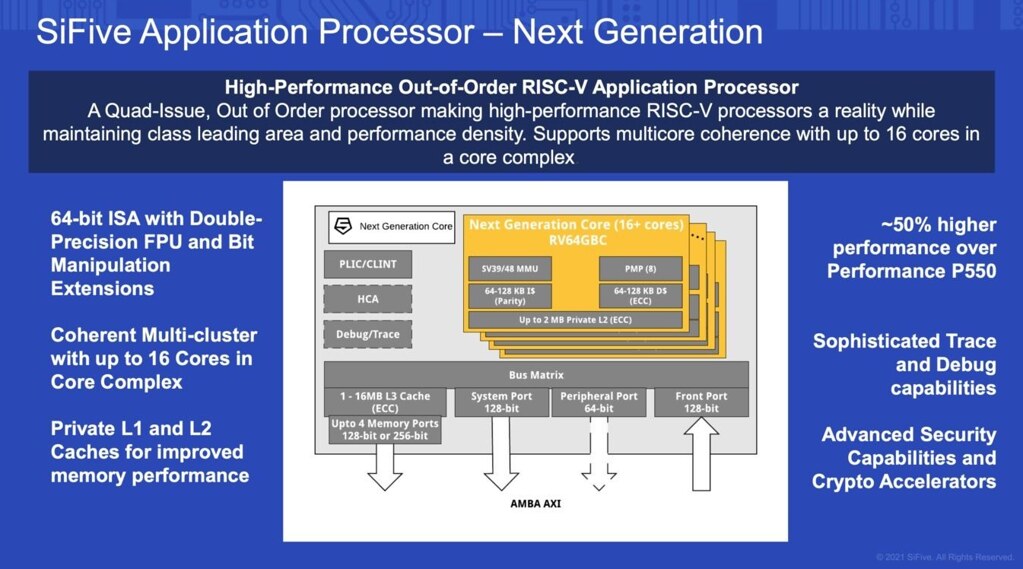

SiFive indiquait en juin que ce SoC P550 était le RISC-V le plus performant du moment. Quatre mois plus tard, la marque indique que son nouveau SoC en cours de développement sera 50% plus rapide et arrivera donc à dépasser la proposition d’ARM avec le Cortex-A78. Cela manque de détails techniques et ce genre de chiffre rond sonne d’un enthousiasme marketing assez classique mais le fait est que l’architecture a clairement du potentiel.

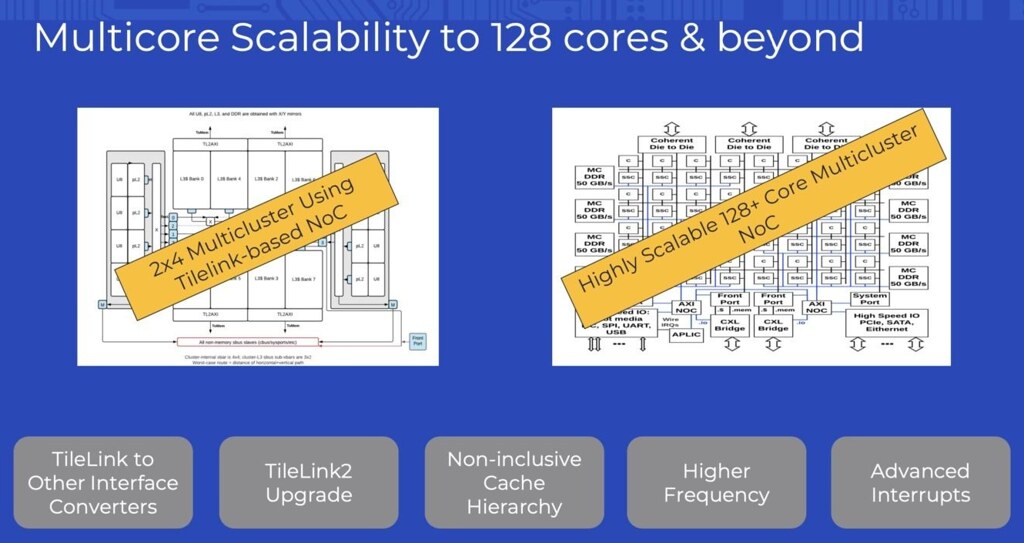

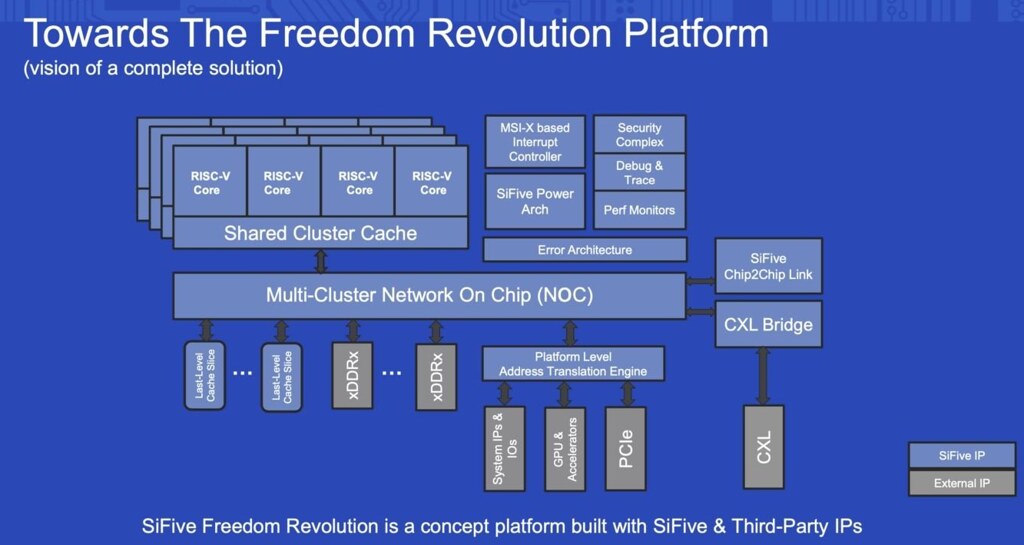

Quelques maigres infos ont été dévoilées en attendant la tenue su RISC-V Summit qui aura lieu en décembre. On sait que la puce sera composée de 16 coeurs et qu’elle tournera à une fréquence allant jusqu’à 3.5 GHz. Elle embarquera 16 Mo de mémoire cache L3 et 2 Mo de cache L2. Ces SoC 64 bits pourront être utilisés en parallèle dans différents profils de machine. De l’ordinateur personnel au serveur en passant par des solutions mobiles ou embarquées. Les solutions les plus performantes fonctionneront comme des clusters de 128 cœurs.

Le potentiel de RISC-V est vraiment intéressant à suivre. De part son architecture très ouverte et libre de toutes royalties, cette technologie intéresse de plus en plus d’acteurs qui y voient un potentiel énorme pour leur futur. Difficile de voir à quel moment cette architecture sera mûre pour le grand public, l’arrivée d’ARM sur les différents secteurs que cette architecture occupe aujourd’hui ne s’est pas faite en un jour, mais une chose est sûre, le potentiel est là.

Le fait que tout le monde puisse fabriquer des processeurs sur mesures par rapport à ses besoins, pourrait être une vraie révolution dans l’approche des outils informatiques.

| 2,5€ par mois | 5€ par mois | 10€ par mois | Le montant de votre choix |

50% plus performant et 5000% plus cher ?

Avec 16 cœurs j’espère bien qu’il est puissant leur processeur.

la puissance theorique c’est une chose mais l’optimisation et les compatibilité c’est autre choses. tout le monde qui fait sa cuisine sans aucune compatibilité logiciels entre les marques ça va chier…. mais bon c’est sur c’est plutot une chose de liberer les architectures.

Le site a un gros probleme sous Firefox depuis quelques semaines. Il s’affiche en format une colonne avec des characteres enorme et des photos floues. Ca ressemble a une version smartphone mais sur une ecran FHD.

Ne pas tenir compte de mon precedent commentaire sur l’affichage du site.. ca venait de moi!

Niveau soft, il y a une debian en cours. Pas sur que l’on puisse avoir une interface graphique mais pour un serveur ca doit passer.

source : https://wiki.debian.org/InstallingDebianOn/SiFive/HiFiveUnmatched#Overall_Status

Personnellement je m’en félicite (c’est à dire je ne râle pas).

Les premières SBC sont trop chères pour moi mais dès que ce sera possible dans les 50€ je testerai.

Il y plein de cas d’usages qui fonctionnent sur du headless.

Si l’Open Source pouvait fonctionner dans ce domaine aussi, ce serait formidable.

L’activité de la Chine sur Risc V est aussi très intéressante, merci Donald, les mesures de restrictions ont favorisé l’intérêt de l’Empire du milieu pour l’autonomie technologique.

La compatibilité logiciel se fait au niveau des sources, et c’est intéressant car une architecture nouvelle ou exotique révéle souvent des bugs. OpenBSD débute aussi sur riscv https://www.openbsd.org/riscv64.html .

je reste un peu dubitatif:

La chine en fait une « arme d’état », pour se sevrer de la dépendance à ARM, mais en bon pays communiste, cette logique n’est pas que purement technologique ou économique (et du coup ne préjuge pas forcément de l’efficacité réelle de ce jeu d’instruction), mais en partie idéologique. Quoi qu’il en soit, cela promet assez vite une déferlante de µC & *P low cost déclinant ce jeu d’instruction chez des acteurs comme Canaan, Gigadevice, etc…

Par contre les « gros » européens historiques l’ayant rejoint très tôt semblent réticents à s’engager dans cette voie : NXP semble avoir lancé un essai relativement timide, tandis que je n’ai pas l’once d’une info sur un dev chez infineon (peut être pas trouvé), et ST Micro, bien qu’attaqué par gigadevice sur ses µC low et medium cost ne semble absolument pas décidé à sortir de la rente de ses Best-sellers STM32 (au demeurant excellents)

Je ne suis pas certain de comprendre pourquoi … la peur de voir le marché être trusté/asséché par les chinois peut être

@Bastien B.:

C’est économique tout simplement: pour l’instant il y a un risque a se jeter sur le marché risc v en volume.

Hors en Chine, c’est politique, l’état chinois poussant des architectures non américaines en avant, pour réduire sa dépendance.

De plus l’état Chinoix contrôle directement ou indirectement la majorité des industries: il peut obliger des entreprises a acheter du risc V , ce qui sécurise les volumes malgré le faite que le marché ne s’y interesse pas.

A noté que le processeur européen (programme EPI) est aussi basé sur RISC-V (ou un mix avec ARM? je sais plus)

@mkpanic:

Ca dénote une certaine frilosité malgré tout. Je n’ai pas regardé ni NXP ni Infineon de près, mais au dernières nouvelles les perfs de ST étaient plus que correctes (sauf si j’ai loupé un épisode) et ce n’est pas lorsqu’on a la tête sous l’eau que le moment est le mieux choisi pour faire de la R&D. GD les attaque sur le bas et moyenne gamme, avec un GD32 qui a ses avantages (fréquence supérieure) et ses inconvénients (temps d’amorçage un poil plus long, flash SPI externe, plus forte conso) et qui se double d’une version RV-32, allégé donc du coût d’une licence ARM

Il y a peut être une raison à ça, comme des pressions de fonds activistes pour augmenter un maximum la rentabilité du titre (et de fait éviter les « mouvements » sans rentabilité immédiate), mais c’est regrettable, et ça risque de se payer au prix fort dans la décennie qui vient

@TiTi:

Un Mix

@Bastien B.: euh pardon correctif, la flash des GD 32 est interne mais sur un substrat séparé

J’ai l’impression qu’un e mes posts a valsé. manifestement deux posts dans un intervalle court pose pb…

@stephane b: Il y a plutôt de belles promesses, côté interopérabilité soft :-)

« « RISC-V a été conçue avec une ISA de base simple et des extensions standard modulaires fixes pour aider à prévenir la fragmentation tout en prenant en charge la personnalisation », avait déclaré Krste Asanovi, président du conseil d’administration de la Fondation RISC-V.« L’écosystème RISC-V a déjà démontré un degré élevé d’interopérabilité entre les différentes implémentations. Maintenant que l’architecture de base a été ratifiée, les développeurs peuvent être assurés que leur logiciel écrit pour RISC-V fonctionnera pour toujours sur tous les cœurs RISC-V similaires », avait-il ajouté. »

https://hardware.developpez.com/actu/318703/L-UE-adopte-l-architecture-RISC-V-sur-supercalculateurs-les-puces-de-22-nm-ont-passe-les-premiers-tests-en-executant-un-programme-hello-world/

Par contre, du côté d’un éventuel rachat par Intel de Sifive, aux dernières nouvelles, ce dernier en a complètement fermé la porte.

« RISC-V a été conçue avec une ISA de base simple » euh heureusement c’est un peu le principe d’un processeur RISC a la base.

Combien de temps avant d’avoir des extension propriétaire ?

16 coeurs a 3,5 GHz, facile d’avoir de la perf avec cette configuration, parlez nous d’IPC même si ça sera moins flatteur.

Pour le code, peut d’optimisation à faire en dehors du compilateur. Ce qui compte pour la performance d’un processeur c’est la gestion des threads, optimisation du cache et parallélisation des unités logiques (entre autre )

Intel, AMD et arm ont qq décennies d’avance sur le sujet, c’est rattrapable mais faudra du temps