Pour graver en 7 nanomètres en utilisant la technologie FinET, il faut compter entre 10 et 12 milliards de dollars d’investissement. Une somme colossale qu’il faut d’abord injecter dans le circuit avant de voir la moindre retombée financière. Le calendrier de cet investissement a en plus le gros désavantage d’être assez long. On ne construit pas une usine de ce type en quelques mois. Il faut donc débourser des sommes énormes sur une longue période de temps avant de rentrer le premier dollar de compensation.

Dans une longue et très intéressante interview accordée à VentureBeat, le PDG de Globalfoundries dévoile ces chiffres et annonce même une augmentation du coût pour construire une usine capable de graver en 5 nanomètres. Les chiffres indiqués sont faramineux, de 14 à 18 milliards de dollars. On comprend mieux pourquoi un fabricant de puces comme Intel commence à bégayer sur ses habitudes de développement en restant pour le moment sur une gravure en 10 nanomètres.

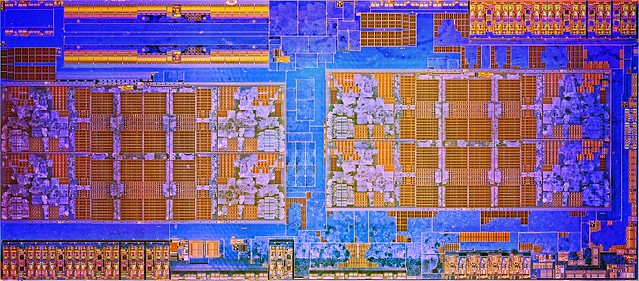

Une Puce AMD Ryzen

Globalfoundries est un des principaux fournisseurs de puces au monde et possède de nombreuses usines. Chacune d’entre elles fabrique pour diverses marques. AMD fait par exemple graver ses puces Ryzen et Radeon chez GF, il faut dire que jusqu’en 2009, Globalfoundries était le fondeur d’AMD avant que celui-ci s’en sépare. La société a évidemment bien d’autres clients comme Qualcomm ou Broadcom. Elle dispose de plusieurs usines à travers le monde. De celle de Dresde en Allemagne qui illustre ce billet à Singapour en passant par les US, le fondeur emploie 18 000 personnes. Ce mastodonte appartient à la Mubadala Development Company PJSC, une entreprise mêlant capitaux publics du gouvernement d’Abu Dhabi des Emirats Arabes unis et des capitaux privés. Sanjay Jha évoque également le coût de développement d’une puce gravée en 7 nanomètres et indique qu’il faut compter entre 250 et 500 millions de dollars pour une seule puce. En prenant un ratio d’investissement de 20% en recherche et développement, il faut que votre société dispose de 2.5 à 5 milliards de dollars de revenus pour se permettre d’en concevoir une nouvelle.

Un constat qui pose problème car si les géant de l’industrie réclament cette possibilité de graver en 7 nanos ou en 5 nanomètres, il faut amortir l’investissement global que l’usine à construire représente. Le souci est que peu de sociétés peuvent s’offrir ces technologies : Apple, Qualcomm, AMD, Nvidia en auront probablement besoin pour continuer à faire évoluer leurs solutions. Mais avec moins d’acteurs, il sera plus difficile d’obtenir un retour sur investissement. La solution serait d’augmenter les tarifs mais cela poserait des soucis de commercialisation des produits finaux aux clients.

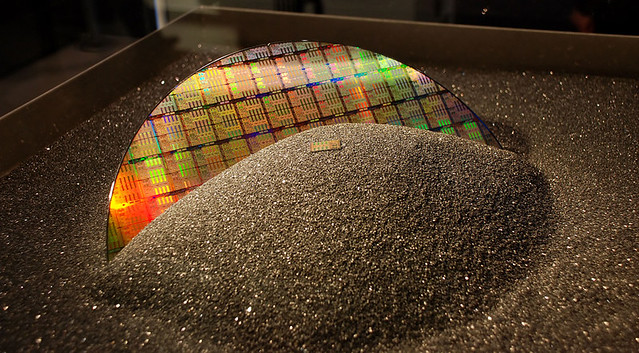

On dit souvent qu’un processeur n’est en réalité qu’un bout de silicium, c’est vrai, même si ce silicium subit des traitement complexes pour devenir une puce, il ne coûte pas une fortune en matière première. Le tarif demandé est donc lié pour le fondeur à l’investissement demandé pour pouvoir le fournir. Et avec des puces 7 nanomètres, ce tarif commence à être difficile à amortir sans un surcoût sensible du prix de chaque puce gravée.

Et cela entraîne un autre constat : Qui va accepter de payer ce surcoût ? Une entreprise qui équipe des salles serveurs verra d’un bon œil une augmentation de performances et une baisse de consommation électrique. En équipant ses serveurs de puces de 10 à 7 nanomètres, elle aura les moyens de l’amortir. Un acheteur de carte graphique très haut de gamme ne sentira peut être pas le surcoût lié à l’évolution de la puce embarquée si sa carte passe de 500 à 550$. L’impact sera noyé dans le prix global de l’objet et sera probablement justifié par une nouvelle architecture aux performances plus impressionnantes. Un acheteur de smartphone très haut de gamme aura lui aussi moins l’impression d’une hausse de tarif de son achat, le prix demandé pour les modèles les plus performants est suffisamment haut pour qu’une augmentation soit plus ou moins « noyée dans la masse ».

Mais il est impossible de viser les puces milieu et entrée de gamme avec cette approche, leur prix serait difficile à justifier pour une gamme de produits finaux abordables. Et cela pose problème à des solutions comme Globalfoundries car construire une usine 7 nanomètres à 10 milliards de dollars pour une gamme limitée de produits chez un nombre limité de clients, cela devient forcément difficile à amortir.

Via : HDBlog.it

| 2,5€ par mois | 5€ par mois | 10€ par mois | Le montant de votre choix |

Faut revenir au morse, c’est beaucoup moins cher :)

10 milliards pour Apple, ce ne doit pas etre vraiment un probleme. Surtout si c’est un investissement pour quelques annees.

C »est quand meme bizarre qu’ils n’arrivent pas a baisser les couts de dabrication des usines elle-memes, avec tous les progres en (nano)robotiques.

Mon Snapdragon 625 gravé en 14nm me suffit amplement… et pour plusieurs années encore !

http://macbidouille.com/news/2017/09/29/tsmc-va-commencer-a-construire-une-usine-destinee-a-la-production-en-3nm

@bunam: La source dit : « Taiwan Semiconductor Manufacturing Company (TSMC) today announced that the company’s planned advanced 3nm fab will be located in the Tainan Science Park in southern Taiwan. »

En gros, ils ont négocié avec Taiwan une aide quelconque qui les a décidé a rester au pays plutôt que de partir aux US pour éviter une éventuelle taxation… Il n’est pas sur qu’ils aient trouvé un terrain vu le problème que cela représente sur place et encore moins commencé a construire quoi que ce soit. Leur fab 7 nano n’est pas encore construite et la news originale indique que selon les plans les plus optimistes le 3 nano serait disponible chez TSMC en 2023. Soit dans 5 à 6 ans suivant la lecture du calendrier. Au vu de ce que cela représente en informatique (et en géopolitique, Trump a le temps de dégager ou de revenir pour un second tour et de bloquer les importations), et pour peu que cela colle à cette vision très optimiste, ces 5 ans pourraient être transformés en 10 ans parce qu’on doit passer le cap des 7 et des 5 nanos qui ne sont toujours pas atteins en mass prod chez TSMC.

En gros on a le temps de voir.

Autrement dit « TSMC va commencer à construire une une usine » c’est à la fois vrai et faux.

« Va commencer » c’est vrai. C’est suffisamment vague. C’est comme quand je dis il va pleuvoir. C’est vrai même si on est en pleine canicule au milieu du désert, un jour il pleuvra. ptet dans 5 ans… Mais un jour il pleuvra.

Un jour ou l’autre probablement TSMC construira une usine 3 nanos… Mais titré comme cela c’est surtout totalement faux car cela semble annoncer un caractère d’urgence…

Franchement la course a la puissance me fatigue. Tout ca pour facebook ou youtube. meh

http://chinawaterrisk.org/resources/analysis-reviews/8-things-you-should-know-about-water-and-semiconductors/

@bunam:

Ci-dessous un copié/collé d’un article dont j’ai perdu le lien, grosso modo le 3nm c’est du bla bla bla commercial.

La finesse de gravure n’est donc plus la taille du plus petit élément d’un composant du circuit intégré, ni même une mesure « physique » précise. C’est un label qui reflète un certain processus de fabrication.

En 2017, la technologie de gravure la plus avancée qui sera disponible sur le marché à grande échelle aura pour nom de code P54M36. Selon l’IRDS, il s’agit d’une « finesse de gravure » de 11/10 nm alors que les Ryzen et Kaby Lake actuels sont en 14 nm.

Cette mesure 11/10nm correspond à un demi-pitch « Fin » de 18 nm et à une largeur « Fin » de 6 nm des microprocesseurs.

Pourquoi introduire la mention « Fin » (aileron en anglais) ? Les choses ont encore changé : les transistors employés par les fondeurs sont désormais en 3D ! Ils sont du type « Fin Field Effect Transistor » (FinFET) et ce depuis 2012, année lors de laquelle Intel les a commercialisés pour la première fois avec sa gamme de microprocesseurs Ivy Bridge en technologie 22 nm. Une évolution qui permet de continuer la course à la miniaturisation des composants.

Plus c’est petit, plus c’est cher…

Pour les puces de milieu et entrée de gamme il y a encore et toujours des « anciennes » gravures moins fines qui sont employées. Aujourd’hui tous les SoC en vente ne sont pas en 10nm, même pour les hauts de gamme de certaines marques.

Il y a des puces très très cher chez Intel, dont le prix n’est pas seulement lié au coût d’une gravure fine.

Les machines nécessaires à la fabrication sont de plus en plus chères, avec des technologies de plus en plus pointues et complexes. La production va enfin démarrer avec des lasers de lithographie « extrême UV » en remplacement des lasers UV, les composants optiques pour ces lasers ne sont plus des lentilles mais des miroirs à incidence rasante. Ces UV extrêmes sont absorbés dans l’air donc il faut tout mettre sous vide. D’ailleurs la moindre particule peut exploser ou faire une ombre et rendre inutilisable la puce.

Si l’on veut graver à 7 nm, il faut positionner le wafer avec une bien meilleure précision tout en bougeant pour graver l’ensemble du wafer en moins d’une minute. Il faut déjà être capable de mesurer la position du wafer avec cette précision dans toutes les directions avant d’appliquer des corrections. Il faut isoler la machine de son environnement extérieur, ça serait bête qu’un opérateur qui marchait à côté fasse trembler le système de 1 nm. La température doit être contrôlée avec une précision extrême puisque la moindre pièce de la machine peut se dilater de bien plus de 1 nm si la température change d’un centième de degré.

A part les grands instruments scientifiques, on trouve dans une fab les machines les plus complexes que l’humanité sache faire.

juste une chose sur la rentabilisation, cette course à la miniaturisation est aussi voulut par les fondeurs à cause de la raréfaction de certains constituant et de l’augmentation des coûts d’approvisionnement.

plus de finesse=plus de puces par wafer, et donc une meilleur rentabilité des galettes qui sortent !

D’après un autre site, lors de cet ITW il parle aussi pas mal du coté commercial entre le 14/12/10/9/7/5nm…. qu’il n’y à pas réellement de différence entre ces modes de gravure.

et c’est vrai que les débats sur le 16nm@Intel VS le 14nm@Samsung VS le 12nm@GF… sont nombreux !!!

il parlent aussi des gros avantage de faire un design spécifique à la gravure !

moi ce qui m’étonne se sont que les alternatives à cette course à la miniaturisation n’est pas vraiment développées (de nouveaux substrats ou autre…).

SOITEC pour ne parler que d’eux est toujours mis en place, 4 ou 5 ans après le démarrage d’une nouvelle ligne !

bon sinon… il est graver en cb notre Rpi3… vivement le 14nm !!! :D

Quand le courant électrique arrachera les électrons, coupant ainsi la liaison électrique entre deux transistors, on aura atteint la limite en finesse de gravure et il faudra trouver autre chose que le silicium.

Y en a qui proposent DES MICROPROCESSEURS EN BOIS :)

Faut toucher du bois (pour que ça marche) !

https://www.science-et-vie.com/technos-et-futur/des-microprocesseurs-en-bois-biodegradables-pour-les-ordinateurs-de-demain-5956

@agumonkey : Eh bien, en réduisant la finesse de gravure d’un facteur k, le temps de propagation est aussi divisé par k, la surface du circuit (et donc son prix de revient) est divisée par k et sa consommation est divisée par k… Donc le circuit est plus rapide, prend moins de place et consomme moins… C’est donc plutôt utile…

Maintenant c’est sûr que si vous en profitez pour mettre k² fois plus de transistors, alors la surface reste la même et la consommation est multipliée par k²/k = k… Et si en plus vous profitez de l’augmentation de la vitesse pour faire tourner des programmes plus lourds, la consommation augmente d’autant…

Mais en soit la diminution des finesses de gravure est donc une bonne chose pour tout le monde, même si, comme moi, vous ne recherchez pas la puissance de calcul.